### Video Genlock PLL

### **General Description**

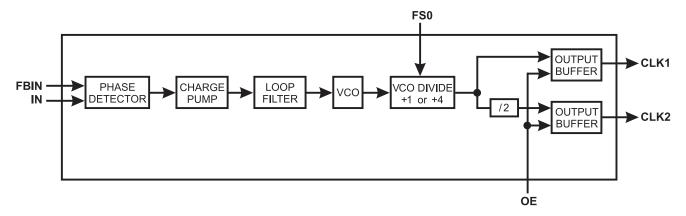

The AV9173-01 provides the analog circuit blocks required for implementing a video genlock dot (pixel) clock generator. It contains a phase detector, charge pump, loop filter, and voltage-controlled oscillator (VCO). By grouping these critical analog blocks into one IC and utilizing external digital functions, performance and design flexibility are optimized as are development time and system cost.

When used with an external clock divider, the AV9173-01 forms a Phase-Locked Loop configured as a frequency synthesizer. The AV9173-01 is designed to accept video horizontal synchronization (h-sync) pulses and produce a video dot clock. A separated, negative-going sync input reference pulse is required at pin 2 (IN).

The AV9173-01 is also suited for other clock recovery applications in such areas as data communications.

#### **Features**

- Phase-detector/VCO circuit block

- Ideal for genlock system

- Reference clock range 25 kHz to 1 MHz for full output clock range

- Input clocks down to 12 kHz possible with restricted output conditions (see Table 1)

- Output clock range 1.25 to 75 MHz

- On-chip loop filter

- Single 5 volt power supply

- Low power CMOS technology

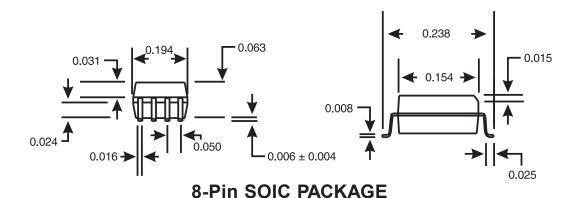

- Small 8-pin DIP or SOIC package

## **Block Diagram**

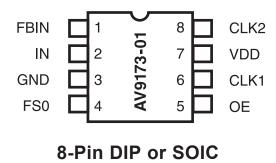

# **Pin Configuration**

## **Pin Descriptions**

| PIN<br>NUMBER | PIN NAME | TYPE   | DESCRIPTION                                |

|---------------|----------|--------|--------------------------------------------|

| 1             | FBIN     | Input  | Feedback Input                             |

| 2             | IN       | Input  | Input for reference sync pulse             |

| 3             | GND      | _      | Ground                                     |

| 4             | FS0      | Input  | Frequency Select 0 input                   |

| 5             | OE       | Input  | Output Enable                              |

| 6             | CLK1     | Output | Clock Output 1                             |

| 7             | VDD      | _      | Power Supply (+5V)                         |

| 8             | CLK2     | Output | Clock Output 2 (Divided-by-2 from Clock 1) |

Table 1: Allowable Input Frequency to Output Frequency (Outputs in MHz)

| f., (1,11,7)                       | four for FS | = 0  (MHz)   | four for $FS = 1$ (MHz) |                |  |

|------------------------------------|-------------|--------------|-------------------------|----------------|--|

| fin (kHz)                          | CLK1 Output | CLK2 Output  | CLK1 Output             | CLK2 Output    |  |

| 12 ≤ fin ≤ 14 kHz                  | 44.0 to 75  | 22.0 to 37.5 | 11.0 to 18.75           | 5.5 to 9.375   |  |

| 14 < fin≤ 17 kHz                   | 30.0 to 75  | 15.0 to 37.5 | 7.5 to 18.75            | 3.75 to 9.375  |  |

| 17 < fin ≤ 30 kHz                  | 25.0 to 75  | 12.5 to 37.5 | 6.25 to 18.75           | 3.125 to 9.375 |  |

| 30 < fin ≤ 35 kHz                  | 15.0 to 75  | 7.5 to 37.5  | 3.75 to 18.75           | 1.875 to 9.375 |  |

| $35 < f_{IN} \le 1000 \text{ kHz}$ | 10.0 to 75  | 5.0 to 37.5  | 2.5 to 18.75            | 1.25 to 9.375  |  |

### Using the AV9173-01

Most video sources, such as video cameras, are asynchronous, free-running devices. To digitize video or synchronize one video source to another free-running reference video source, a video "genlock" (generator lock) circuit is required. The **AV9173-01** integrates the analog blocks which make the task much easier.

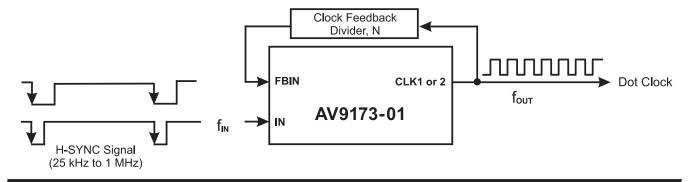

In the complete video genlock circuit, the primary function of the AV9173-01 is to provide the analog circuitry required to generate the video dot clock within a PLL. This application is illustrated in Figure 1. The input reference signal for this circuit is the horizontal synchronization (h-sync) signal. If a composite video reference source is being used, the h-sync pulses must be separated from the composite signal. A video sync separator circuit, such as the National Semiconductor LM1881, can be used for this purpose.

The clock feedback divider shown in Figure 1 is a digital divider used within the PLL to multiply the reference frequency. Its divide ratio establishes how many video dot clock cycles occur per h-sync pulse. For example, if 880 pixel clocks are desired per h-sync pulse, then the divider ratio is set to 880. Hence, together the h-sync frequency and external divider ratio establish the dot clock frequency:

$f_{OUT} = f_{IN} \cdot N$  where N is external divide ratio

Both AV9173-01 input pins IN and FBIN respond only to negative-going clock edges of the input signal. The h-sync signal must be constant frequency in the 25 kHz to 1MHz range and stable (low clock jitter) for creation of a stable output clock.

Refer to Application Brief (AB01) for additional details on use of input frequencies below 25kHz. By following the guidelines in this brief and meeting the test conditions in the

AC specifications (VCO frequency), an input as low as 12kHz (such as NTSC or PAL h-sync) can be used.

The output hook-up of the **AV9173-01** is dictated by the desired dot clock frequency. The primary consideration is the internal VCO which operates over a frequency range of 10 MHz to 75 MHz. Because of the selectable VCO output divider and the additional divider on output CLK2, four distinct output frequency ranges can be achieved. The following Table lists these ranges and the corresponding device configuration.

| FS0 State | Output Used | Frequency Range  |

|-----------|-------------|------------------|

| 0         | CLK1        | 10 - 75 MHz      |

| 0         | CLK2        | 5 - 37.5 MHz     |

| 1         | CLK1        | 2.5 - 18.75 MHz  |

| 1         | CLK2        | 1.25 - 9.375 MHz |

Note that both outputs, CLK1 and CLK2, are available during operation even though only one is fed back via the external clock divider.

Pin 5, OE, tristates both CLK1 and CLK2 upon logic low input. This feature can be used to revert dot clock control to the system clock when not in genlock mode (hence, when in genlock mode the system dot clock must be tristated).

When unused, inputs FS0 and OE must be tied to either GND (logic low) or VDD (logic high).

For further discussion of VCO/PLL operation as it applies to the **AV9173-01**, please refer to the AV9170 application note. The AV9170 is a similar device with fixed feedback dividers for skew control applications.

Figure 1: Typical Application of AV9173-01 in a Video Genlock System

### **Absolute Maximum Ratings**

$V_{DD}$  (referenced to GND)................................ 7.0 V

Operating Temperature under Bias . . . . . . . 0°C to +70°C

Storage Temperature . . . . . . . . . . . .  $-65^{\circ}$ C to  $+150^{\circ}$ C

Voltage on I/O pins referenced to GND . . . . . GND -0.5 V to  $V_{DD} + 0.5$  V

Power Dissipation . . . . . . . . . . . . . . . . 0.5 watts

Stresses above those listed under *Absolute Maximum Ratings* above may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those listed in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect product reliability.

#### **Electrical Characteristic**

$V_{DD} = +5V \pm 5\%$ ,  $T_A = 0$ °C to 70°C, unless otherwise stated

| DC CHARACTERISTICS               |        |                                     |           |     |     |       |  |

|----------------------------------|--------|-------------------------------------|-----------|-----|-----|-------|--|

| PARAMETER                        | SYMBOL | TEST CONDITIONS                     | MIN       | TYP | MAX | UNITS |  |

| Input Low Voltage                | VIL    | $V_{DD} = 5V$                       | _         |     | 0.8 | V     |  |

| Input High Voltage               | Vih    | $V_{DD} = 5V$                       | 2.0       |     | _   | V     |  |

| Input Low Current                | IIL    | $V_{IN} = 0V$                       | -5        |     |     | μΑ    |  |

| Input High Current               | Іін    | $V_{IN} = V_{DD}$                   | -5        |     | 5   | μA    |  |

| Output Low Voltage <sup>1</sup>  | Vol    | IOL = 8mA                           | _         |     | 0.4 | V     |  |

| Output High Voltage <sup>1</sup> | Vон1   | IOH = -1mA,  VDD = 5.0V             | VDD -0.4V |     | _   | V     |  |

| Output High Voltage <sup>1</sup> | Vон2   | $I_{OH} = -4mA,$<br>$V_{DD} = 5.0V$ | VDD -0.8V |     |     | V     |  |

| Output High Voltage <sup>1</sup> | Vон3   | IOH = -8mA                          | 2.4       | _   | _   | V     |  |

| Supply Current                   | Idd    | Unloaded, 50 MHZ                    |           | 20  | 50  | mA    |  |

#### **Notes:**

- 1. Duty cycle measured at 1.4V.

- 2. Input Reference Frequency = 25 kHz, Output Frequency = 25 MHz. Jitter measured between adjacent vertical pixels.

- 3. CLK1 frequency applies for FS = 0. For FS = 1 condition, divide allowable CLK1 range by the factor of 4.

#### **Electrical Characteristics**

$V_{DD} = +5V \pm 5\%$ ,  $T_A = 0$ °C to 70°C, unless otherwise stated

| AC CHARACTERISTICS                         |                   |                                 |      |      |      |       |

|--------------------------------------------|-------------------|---------------------------------|------|------|------|-------|

| PARAMETER                                  | SYMBOL            | TEST CONDITIONS                 | MIN  | TYP  | MAX  | UNITS |

| Input Clock Rise Time <sup>1</sup>         | ICLKr             |                                 |      | _    | 10   | ns    |

| Input Clock Fall Time <sup>1</sup>         | ICLKf             |                                 | _    | _    | 10   | ns    |

| Output Rise Time <sup>1</sup>              | tr1               | 15pF load; 0.8 to 2.0V          |      | 0.6  | 1.5  | ns    |

| Output Rise time <sup>1</sup>              | tr2               | 15pF load;<br>20% to 80% VDD    | _    | 1.6  | 3.0  | ns    |

| Output Fall time <sup>1</sup>              | <b>t</b> f1       | 15pF load; 2.0 to 0.8V          |      | 1.0  | 2.0  | ns    |

| Output Fall time <sup>1</sup>              | tf2               | 15pF load;<br>80% to 20% VDD    | _    | 0.9  | 2.0  | ns    |

| Output Duty Cycle <sup>1</sup>             | dt                | 15pF load                       | 40   | 47   | 55   | %     |

| Jitter, one sigma <sup>1</sup>             | T1s1              | CLK1 frequency≥ 25 MHz          |      | 120  | 250  | ps    |

| Jitter, absolute <sup>1</sup>              | Tabs 1            | CLK1 frequency≥ 25 MHz          | -400 | ±250 | 400  | ps    |

| Jitter, one sigma <sup>1</sup>             | T1s2              | CLK1 frequency< 25 MHz          | _    | _    | 1    | %     |

| Jitter, absolute <sup>1</sup>              | Tabs 2            | CLK1 frequency< 25 MHz          | _    | _    | 2    | %     |

| Line-to-line jitter, absolute <sup>2</sup> | TLabs             |                                 | _    | ±4   | _    | ns    |

| Input Frequency, IN or FBIN                | fi                | See allowable fi below:         | 12   | _    | 1000 | kHz   |

|                                            |                   | $12 \le f_i \le 14 \text{ kHz}$ | 44.0 |      | 75   | MHz   |

|                                            |                   | $14 < f_i \le 17 \text{ kHz}$   | 30.0 | _    | 75   | MHz   |

| CLK1 Frequency <sup>1, 3, 4</sup>          | f <sub>CLK1</sub> | 17 < fi ≤ 30 kHz                | 25.0 | _    | 75   | MHz   |

|                                            |                   | $30 < f_i \le 35 \text{ kHz}$   | 15.0 |      | 75   | MHz   |

|                                            |                   | 35 < fi ≤ 1000 kHz              | 10.0 | _    | 75   | MHz   |

#### **Notes:**

- $1. \ \ Parameter is guaranteed by design and characterization. Not 100\% tested in production.$

- 2. Input Reference Frequency = 25 kHz, Output Frequency = 25 MHz. Jitter measured between adjacent vertical pixels.

- 3. CLK1 frequency applies for FS = 0. For FS = 1 condition, divide allowable CLK1 range by the factor of 4.

- 4. An Application Brief (AB01) documents the operation of the AV9173 for low input frequencies. This provides guidelines for usable output frequencies and feedback ratios required to use inputs below 25 kHz. By following these guidelines, the AV9173 will operate down to 12 kHz inputs across temperature, voltage and lot-to-lot variation.

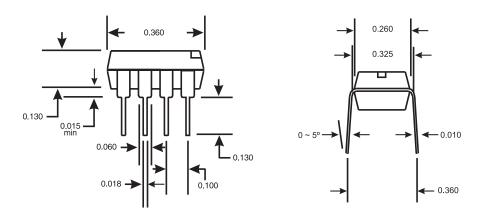

#### 8-Pin DIP PACKAGE

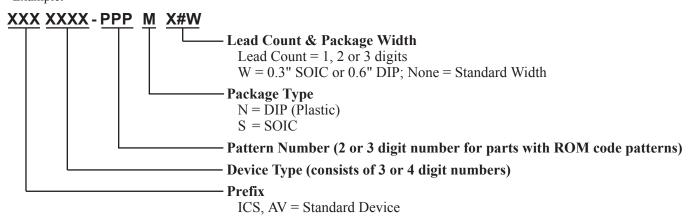

## **Ordering Information**

AV9173-01CN08 - or - AV9173-01CS08

Example:

# This datasheet has been download from:

www.datasheetcatalog.com

Datasheets for electronics components.