# **BMA400**Digital, triaxial acceleration sensor

**Bosch Sensortec**

#### **Preliminary Data Sheet BMA400**

Part number(s) 0 273 141 xyz

Document revision 0.1

Release date 03 November 2017

Document number BST-BMA400-DS000-00

Notes Specifications are preliminary and subject to change without notice.

Product photos and pictures are for illustration purposes only and may

differ from the real product's appearance.

Preliminary Data Sheet - Confidential and under NDA

Page 2 / Confidential

### **BMA400**

12 bit, digital, triaxial acceleration sensor with smart on-chip motion and position-triggered interrupt features.

### **Key features**

• Small package size LGA package (12 pins), footprint 2mm x 2mm,

height 0.95 mm

Ultra-low power

Low current consumption of data acquisition

without compromising on performance (< 14 µA with highest performance)

Programmable functionality

Acceleration ranges ±2g/±4g/±8g/±16g

Low-pass filter bandwidths = 0.48\*ODR up to a max. output data read out of 800Hz

On-chip FIFO

Integrated FIFO on sensor with 1 kb

On-chip interrupt features

Auto-low power/Auto wakeup

Activity/In-activit

Step Counter (4µA)

Activity Recognition (Walking, Running, Standing still)

Orientation detection Tap/double tap

Digital interface SPI (4-wire, 3-wire), I<sup>2</sup>C, 2 interrupt pins

V<sub>DDIO</sub> voltage range: 1.2V to 3.6V

RoHS compliant, halogen-free

#### **Typical applications**

- Step Counting with ultra-low current consumption for extensive battery lifetime

- Advanced system power management for mobile applications and (smart) watches

- Fitness applications / Activity Tracking

- Tap / double tap sensing

- Drop detection for warranty logging

- Window/door measurements for climate control and alarm systems

- IoT applications powered by coin cell driven batteries, requiring <1uA and auto-wakeup functionality</li>

BST-BMA400-DS000-00 | Version 0.1 | November 2017

Page 3 / Confidential

### **Table of contents**

### **Contents**

| 1. | SPECIFICATION                                  | 8         |

|----|------------------------------------------------|-----------|

| 2. | ABSOLUTE MAXIMUM RATINGS                       | 10        |

| 3. | QUICK START GUIDE                              | 11        |

|    | Note about using the BMA400:                   |           |

|    | First application setup examples algorithms:   |           |

| 4. | FUNCTIONAL DESCRIPTION                         |           |

|    | 4.1. SUPPLY VOLTAGE AND POWER MANAGEMENT       | 1.5       |

|    |                                                |           |

| 4  | 4.2. POWER MODES – PERFORMANCE MODES           |           |

|    | Auto low-power mode                            | 2         |

|    |                                                | 2         |

| 4  | 4.3. SENSOR DATA                               | 26        |

|    | Filter Configuration                           | 25<br>کا  |

| X  | G-range selection                              | 20<br>20  |

|    | Data Ready Interrupt                           | 29        |

|    | Temperature Sensor                             | 29        |

|    | Sensor Time                                    | 30        |

| Δ  | 4.4. FIFO                                      | 31        |

| ,  | FIFO description                               | 3.1       |

|    | FIFO input data                                | 31        |

|    | FIFO read out                                  | 32        |

|    | FIFO overflow behavior                         | 32        |

|    | Frames                                         | 33        |

|    | Under-read                                     | 36        |

|    | Partial frame read                             |           |

|    | Over-readReading nearly-empty FIFO             | اک<br>برد |

|    | FIFO flushing                                  | ع<br>ع    |

|    | FIFO watermark interrupt                       |           |

|    | FIFO full interrupt                            | 39        |

| _  | 4.5. GENERAL INTERRUPT PIN CONFIGURATION       |           |

| 7  | Interrupt Pin Mapping                          | 40        |

|    | Interrupt Pin MappingInterrupt latching        | 40        |

|    | Interrupt behavior during power mode switching |           |

|    | Electrical Interrupt Pin Behavior              |           |

| 4  | 4.6. Interrupt Features                        | 43        |

Page 4 / Confidential

| li   | nterrupt pin mapping, interrupt status                                            | 43 |

|------|-----------------------------------------------------------------------------------|----|

| (    | Generic Interrupt 1 and 2                                                         | 44 |

|      | Step Detector / Step Counter                                                      |    |

| A    | Activity changed interrupt                                                        | 48 |

|      | Tap Sensing Interrupt                                                             |    |

|      | nterrupt engine overrun                                                           |    |

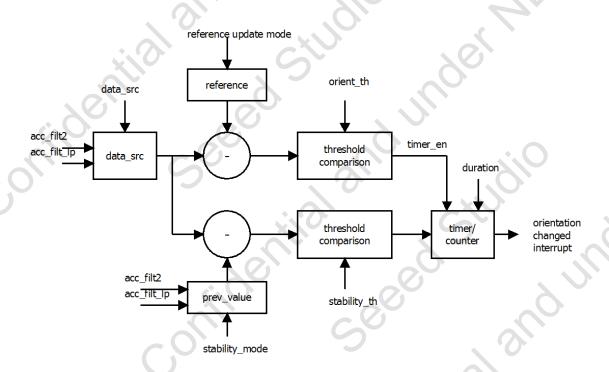

| C    | Orientation change interrupt                                                      | 51 |

| 4.7  |                                                                                   |    |

| 4.8  | . Soft-Reset                                                                      | 55 |

| 5. F | REGISTER DESCRIPTION                                                              | 56 |

| 5.1. | . Register Map                                                                    | 56 |

| F    | Register (0x00) CHIPID                                                            | 59 |

| F    | Register (0x00) CHIPIDRegister (0x02) ERR_REG                                     | 60 |

| F    | Register (0x03) STATUS                                                            | 60 |

| F    | Register (0x04) ACC, X, LSB                                                       | 61 |

| F    | Register (0x05) ACC_X_MSB                                                         | 62 |

| F    | Register (0x06) ACC Y LSB                                                         | 62 |

| F    | Register (0x07) ACC_Y_MSB                                                         | 63 |

| F    | Register (0x08) ACC_Z_LSB                                                         | 63 |

|      | Register (0x09) ACC_Z_MSB                                                         |    |

|      | Register (0x0A) SENSOR_TIME0                                                      |    |

| F    | Register (0x0B) SENSOR_TIME1                                                      | 65 |

| F    | Register (0x0C) SENSOR_TIME2                                                      | 65 |

| F    | Register (0x0D) EVENT                                                             | 66 |

| F    | Register (0x0E) INT_STAT0                                                         | 66 |

| F    | Register (0x0F) INT_STAT1                                                         | 67 |

| F    | Register (0x10) INT_STAT2                                                         | 68 |

| F    | Register (0x11) TEMP_DATA                                                         | 68 |

| F    | Register (0x12) FIFO_LENGTH0                                                      | 69 |

| F    | Register (0x13) FIFO_LENGTH1                                                      | 69 |

| F    | Register (0x14) FIFO_DATA                                                         | 70 |

| F    | Register (0x14) FIFO_DATA<br>Register (0x15) STEP_CNT_0                           | 70 |

| F    | Register (0x16) STEP_CNT_1Register (0x17) STEP_CNT_2                              | 71 |

| F    | Register (0x17) STEP_CNT_2                                                        | 71 |

| F    | Register (0x18) STEP STAT                                                         | 72 |

| F    | Register (0x19) ACC CONFIG0                                                       | 72 |

| F    | Register (0x1A) ACC_CONFIG1                                                       | 73 |

| F    | Register (0x1A) ACC_CONFIG1Register (0x1B) ACC_CONFIG2Register (0x1F) INT_CONFIG0 | 74 |

| F    | Register (0x1F) INT_CONFIG0                                                       | 74 |

| F    | Register (0x20) INT_CONFIG1Register (0x21) INT1_MAP                               | 75 |

| F    | Register (0x21) INT1_MAP                                                          | 75 |

| F    | Register (0x22) INT2_MAP                                                          | 76 |

|      | Register (0x23) INT12_MAP                                                         |    |

| F    | Register (0x24) INT12_IO_CTRL                                                     | 78 |

Page 5 / Confidential

| Register (0x26) FIFO_CONFIG0     | 79  |

|----------------------------------|-----|

| Register (0x27) FIFO_CONFIG1     | 80  |

| Register (0x28) FIFO_CONFIG2     |     |

| Register (0x29) FIFO_PWR_CONFIG  | 81  |

| Register (0x2A) AUTOLOWPOW_0     |     |

| Register (0x2B) AUTOLOWPOW_1     | 82  |

| Register (0x2C) AUTOWAKEUP_0     |     |

| Register (0x2D) AUTOWAKEUP_1     | 83  |

| Register (0x2F) WKUP_INT_CONFIG0 | 84  |

| Register (0x30) WKUP_INT_CONFIG1 | 85  |

| Register (0x31) WKUP_INT_CONFIG2 |     |

| Register (0x32) WKUP_INT_CONFIG3 |     |

| Register (0x33) WKUP_INT_CONFIG4 | 86  |

| Register (0x35) ORIENTCH_CONFIG0 | 87  |

| Register (0x36) ORIENTCH_CONFIG1 | 88  |

| Register (0x37) ORIENTCH_CONFIG2 |     |

| Register (0x38) ORIENTCH_CONFIG3 | 89  |

| Register (0x39) ORIENTCH_CONFIG4 | 89  |

| Register (0x3A) ORIENTCH_CONFIG5 | 90  |

| Register (0x3B) ORIENTCH_CONFIG6 | 90  |

| Register (0x3C) ORIENTCH_CONFIG7 |     |

| Register (0x3D) ORIENTCH_CONFIG8 | 91  |

| Register (0x3E) ORIENTCH_CONFIG9 | 92  |

| Register (0x3F) GEN1INT_CONFIG0  | 92  |

| Register (0x40) GEN1INT_CONFIG1  | 93  |

| Register (0x41) GEN1INT_CONFIG2  | 94  |

| Register (0x42) GEN1INT_CONFIG3  |     |

| Register (0x43) GEN1INT_CONFIG31 | 95  |

| Register (0x44) GEN1INT_CONFIG4  | 95  |

| Register (0x45) GEN1INT_CONFIG5  | 96  |

| Register (0x46) GEN1INT_CONFIG6  |     |

| Register (0x47) GEN1INT_CONFIG7  |     |

| Register (0x48) GEN1INT_CONFIG8  | 97  |

| Register (0x49) GEN1INT_CONFIG9  | 98  |

| Register (0x4A) GEN2INT_CONFIG0  | 98  |

| Register (0x4B) GEN2INT_CONFIG1  | 99  |

| Register (0x4C) GEN2INT_CONFIG2  | 100 |

| Register (0x4D) GEN2INT_CONFIG3  | 100 |

| Register (0x4E) GEN2INT_CONFIG31 | 101 |

| Register (0x4F) GEN2INT_CONFIG4  |     |

| Register (0x50) GEN2INT_CONFIG5  | 102 |

| Register (0x51) GEN2INT_CONFIG6  |     |

| Register (0x52) GEN2INT_CONFIG7  |     |

| Register (0x53) GEN2INT_CONFIG8  |     |

| Register (0x54) GEN2INT CONFIG9  | 104 |

Page 6 / Confidential

| Re          | gister (0x55) ACTCH CONFIG0                                            | . 104 |

|-------------|------------------------------------------------------------------------|-------|

|             | gister (0x56) ACTCH_CONFIG1                                            |       |

|             |                                                                        |       |

| Re          | gister (0x57) TAP_CONFIGgister (0x58) TAP_CONFIG1                      | . 106 |

| Re          | gister (0x59) STEP_COUNTER_CONFIG0                                     | . 108 |

| Re          | gister (0x5A) STEP_COUNTER_CONFIG1                                     | . 108 |

|             | gister (0x5B) STEP_COUNTER_CONFIG2                                     |       |

|             | gister (0x5C) STEP_COUNTER_CONFIG3                                     |       |

|             | gister (0x5D) STEP_COUNTER_CONFIG4                                     |       |

|             | gister (0x5E) STEP_COUNTER_CONFIG5                                     |       |

|             | gister (0x5F) STEP_COUNTER_CONFIG6                                     |       |

|             | gister (0x60) STEP_COUNTER_CONFIG7                                     |       |

|             | gister (0x61) STEP_COUNTER_CONFIG8                                     |       |

| Re          | gister (0x62) STEP_COUNTER_CONFIG9                                     | . 112 |

| Re          | gister (0x63) STEP_COUNTER_CONFIG10                                    | . 113 |

|             | gister (0x64) STEP_COUNTER_CONFIG11                                    |       |

| Re          | gister (0x65) STEP_COUNTER_CONFIG12                                    | . 114 |

|             | gister (0x66) STEP_COUNTER_CONFIG13                                    |       |

| Re          | gister (0x67) STEP_COUNTER_CONFIG14                                    | . 115 |

| Re          | gister (0x68) STEP_COUNTER_CONFIG15                                    | . 115 |

| Re          | gister (0x69) STEP_COUNTER_CONFIG16                                    | . 116 |

| Re          | gister (0x6A) STEP_COUNTER_CONFIG17gister (0x6B) STEP_COUNTER_CONFIG18 | . IIC |

| Re          | gister (0x6C) STEP_COUNTER_CONFIG18                                    | 117   |

| Do          | gister (0x6C) STEP_COUNTER_CONFIG19                                    | 110   |

| Po          | gister (0x0D) STEP_COUNTER_CONFIG20                                    | 110   |

| Re          | gister (0x6E) STEP_COUNTER_CONFIG21gister (0x6F) STEP_COUNTER_CONFIG22 | 110   |

| Re          | gister (0x70) STEP_COUNTER_CONFIG23                                    | 110   |

| Re          | gister (0x70) STEP_COUNTER_CONFIG24                                    | 120   |

| Re          | gister (0x7C) IF_CONF                                                  | 120   |

| Re          | gister (0x7D) SELF_TEST                                                | 121   |

| Re          | gister (0x7E) CMD                                                      | 122   |

|             | GITAL INTERFACES                                                       | 400   |

| DIC         | #ITAL INTERFACES                                                       |       |

| <b>3.1.</b> | INTERFACE                                                              | .123  |

| 6.2.        | INTERFACE I2C/SPI PROTOCOL SELECTION                                   | .124  |

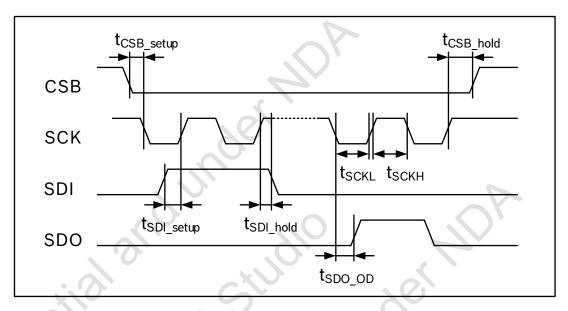

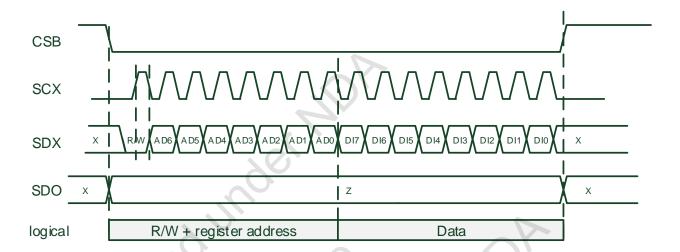

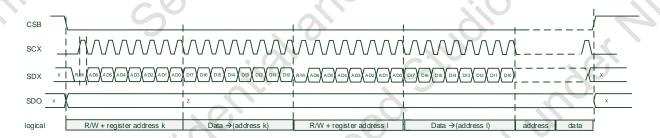

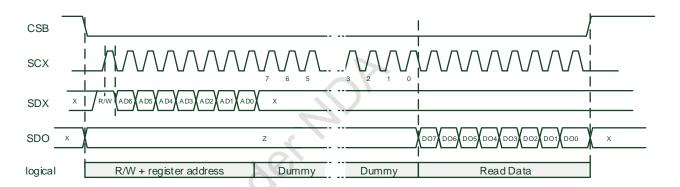

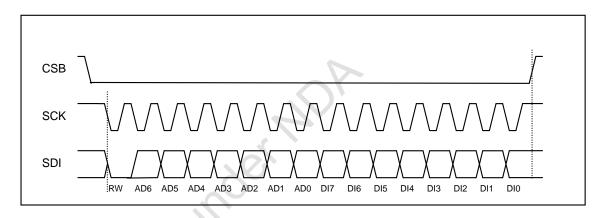

| 6.3.        | SPI INTERFACE AND PROTOCOL                                             | .124  |

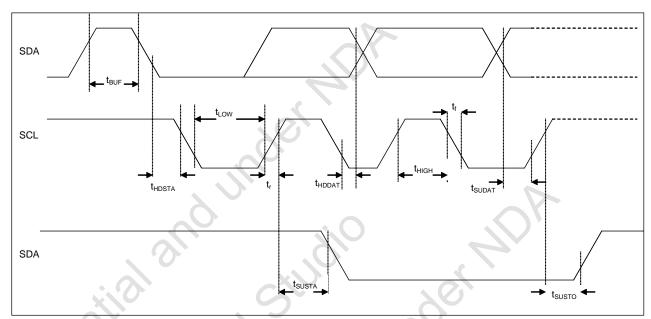

| 6.4.        | PRIMARY I2C INTERFACE                                                  | .129  |

| -           | read access:                                                           |       |

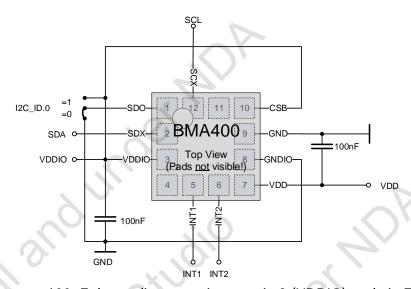

| PII         | -OUT AND CONNECTION DIAGRAMS                                           | .133  |

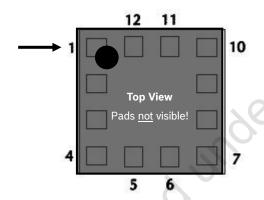

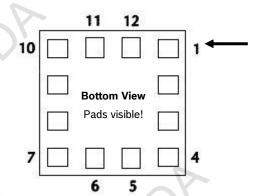

| 7.1.        | PIN-OUT                                                                | .133  |

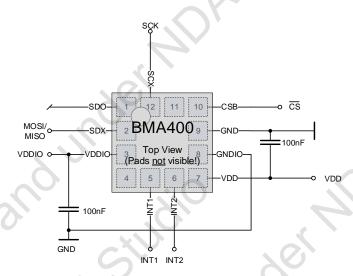

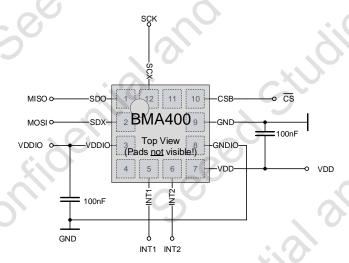

| 7.2.        | CONNECTION DIAGRAMS                                                    | .134  |

|             | CONNECTION DIAGRAMS                                                    |       |

|             |                                                                        |       |

|             |                                                                        |       |

6.

7.

Page 7 / Confidential

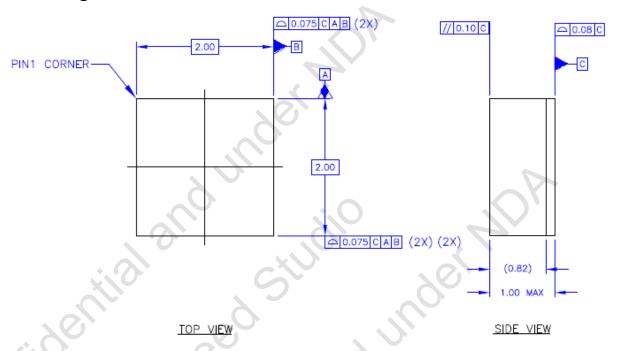

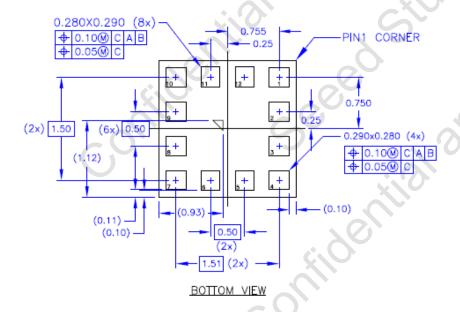

| 8. PA                                    | CKAGE                           | 136 |  |  |  |

|------------------------------------------|---------------------------------|-----|--|--|--|

| 8.1.                                     | PACKAGE OUTLINE DIMENSIONS      | 136 |  |  |  |

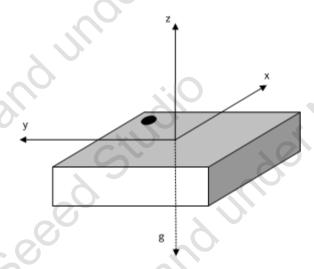

| 8.2.                                     | SENSING AXIS ORIENTATION        | 137 |  |  |  |

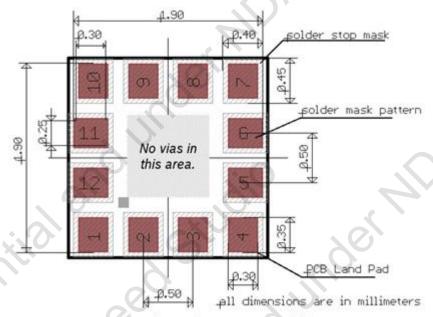

| 8.3.                                     | LANDING PATTERN RECOMMENDATION  | 139 |  |  |  |

| 8.4.                                     | Marking                         | 140 |  |  |  |

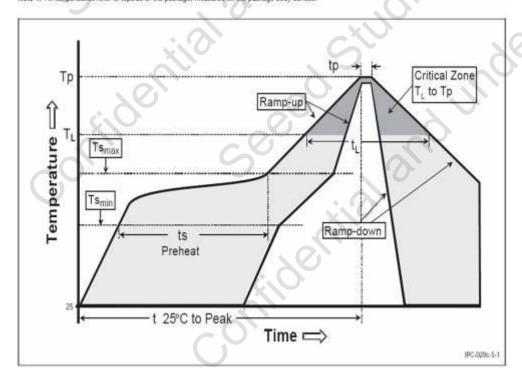

| 8.5.                                     | SOLDERING GUIDELINES            | 141 |  |  |  |

| 8.6.                                     | HANDLING INSTRUCTIONS           |     |  |  |  |

| 8.7. ENVIRONMENTAL SAFETYHalogen content |                                 | 143 |  |  |  |

|                                          | GAL DISCLAIMER                  |     |  |  |  |

| 9.1. EN                                  | .1. ENGINEERING SAMPLES144      |     |  |  |  |

| 9.2. PR                                  | ODUCT USE                       | 144 |  |  |  |

|                                          | PLICATION EXAMPLES AND HINTS    |     |  |  |  |

| 10. DO                                   | CUMENT HISTORY AND MODIFICATION | 145 |  |  |  |

Page 8 / Confidential

### 1. Specification

Unless stated otherwise, the given values are over lifetime, operating temperature and voltage ranges. Minimum/maximum values are  $\pm 3\sigma$ .

#### Parameter Specification

| Parameter                                       | Symbol          | Condition                                            | Min                   | Тур | Max                   |    |

|-------------------------------------------------|-----------------|------------------------------------------------------|-----------------------|-----|-----------------------|----|

| Acceleration                                    | <b>g</b> FS2g   |                                                      |                       | ±2  |                       | g  |

| Range                                           | <b>g</b> FS4g   | 70,                                                  |                       | ±4  |                       | g  |

|                                                 | <b>g</b> FS8g   | 10,                                                  |                       | ±8  |                       | g  |

|                                                 | <b>g</b> FS16g  |                                                      |                       | ±16 |                       | g  |

| Supply Voltage<br>Internal<br>Domains           | $V_{DD}$        | 11                                                   | 1.72                  | 1.8 | 3.6                   | V  |

| Supply Voltage I/O Domain                       | $V_{DDIO}$      |                                                      | 1.2                   | 1.8 | 3.6                   | V  |

| Voltage Input<br>Low Level                      | V <sub>IL</sub> | SPI & I <sup>2</sup> C                               |                       | (0) | 0.3V <sub>DDIO</sub>  |    |

| Voltage Input<br>High Level                     | V <sub>IH</sub> | SPI & I <sup>2</sup> C                               | 0.7V <sub>DDIO</sub>  |     |                       |    |

| Voltage Output<br>Low Level                     | V <sub>OL</sub> | $V_{DDIO}$ =1.8V, $I_{OL}$ =3mA, SPI                 | 6                     |     | 0.2V <sub>DDIO</sub>  |    |

|                                                 | 50              | $V_{DDIO}$ =1.2V, $I_{OL}$ =3mA, SPI                 |                       | 16. | 0.23V <sub>DDIO</sub> | -  |

| Voltage Output<br>High Level                    | $V_{OH}$        | $V_{DDIO}$ =1.8V, $I_{OH}$ =3mA, SPI                 | 0.8V <sub>DDIO</sub>  | CKI |                       | 0  |

|                                                 |                 | $V_{DDIO}$ =1.2V, $I_{OH}$ =3mA, SPI                 | 0.62V <sub>DDIO</sub> |     |                       |    |

| Total Supply<br>Current in<br>Normal mode       | IDD             | Nominal VDD and<br>VDDIO, 25°C,<br>OSR=3             | 200                   | 14  | 900                   | μΑ |

| Total Supply<br>Current in<br>Sleep Mode        | IDDsum          | Nominal VDD and VDDIO, 25°C                          |                       | 200 |                       | nA |

| Total Supply<br>Current in<br>Low-power<br>Mode | IDDlp1          | Nominal VDD and<br>VDDIO, 25°C<br>25 Hz ODR<br>OSR=0 | 100                   | 800 |                       | nA |

| Wake-Up Time                                    | tw_up           | From sleep to normal mode                            | (10)                  |     | 2/ODR                 |    |

| Power-Up Time                                   | ts_up           | Starting the device to sleep mode                    |                       |     | 1                     | ms |

| Operating<br>Temperature                        | TA              | O                                                    | -40                   |     | +85                   | °C |

BST-BMA400-DS000-00 | Version 0.1 | November 2017

<sup>©</sup> Bosch Sensortec GmbH reserves all rights even in the event of industrial property rights. We reserve all rights of disposal such as copying and passing on to third parties. BOSCH and the symbol are registered trademarks of Robert Bosch GmbH, Germany.

Note: Specifications within this document are subject to change without notice.

Page 9 / Confidential

| OUTPUT SIGNAL                         |                     |                                                                                                |             |           |          |        |

|---------------------------------------|---------------------|------------------------------------------------------------------------------------------------|-------------|-----------|----------|--------|

| Parameter                             | Symbol              | Condition                                                                                      | Min         | Тур       | Max      | Units  |

| Sensitivity                           | S <sub>2g</sub>     | g <sub>FS2g</sub> , T <sub>A</sub> =25°C                                                       |             | 1024      |          | LSB/g  |

|                                       | S <sub>4g</sub>     | $g_{FS4g}$ , $T_A=25$ °C                                                                       |             | 512       |          | LSB/g  |

|                                       | S <sub>8g</sub>     | $g_{FS8g}$ , $T_A=25^{\circ}C$                                                                 |             | 256       |          | LSB/g  |

|                                       | S <sub>16g</sub>    | $g_{FS16g}$ , $T_A=25$ °C                                                                      |             | 128       |          | LSB/g  |

| Sensitivity<br>Temperature<br>Drift   | TCS                 | 7110                                                                                           |             | 0.02      |          | %/K    |

| Zero-g Offset                         | Off                 | Nominal $V_{DD}$ and $VDD_{IO}$ , 25°C, $g_{FS4g}$ Over life-time                              |             | 80        |          | mg     |

| Zero-g Offset<br>Temperature<br>Drift | тсо                 | Cillo                                                                                          |             |           |          | mg/K   |

| Output Data<br>Rate                   | ODR <sub>NORM</sub> | Normal mode                                                                                    | 12.5        | <b>)</b>  | 800      | Hz     |

| Bandwidth                             | BWnorm              | 3dB cutoff<br>frequency of the<br>accelerometer is<br>selectable                               | 0.24*ODR    | <i>\\</i> | 0.48*ODR | Hz     |

| Output Data<br>Rate                   | $ODR_{LPM}$         | Low-power mode                                                                                 |             | 25        |          | Hz     |

| Nonlinearity                          | NL                  | Nominal V <sub>DD</sub> and VDD <sub>IO</sub> , 25°C, g <sub>FS4g</sub>                        |             | 0.5       |          | %FS    |

| Output Noise<br>Density               | n <sub>rms</sub>    | Typical V <sub>DD</sub> and VDD <sub>IO</sub> , normal mode, OSR=3 (high performance) 25°C, 4g | 000         | 220       | 9 nu     | µg/√Hz |

|                                       | 0                   | MECHANICAL CHAP                                                                                | RACTERISTIC | s         |          |        |

| Parameter                             | Symbol              | Condition                                                                                      | Min         | Тур       | Max      | Units  |

| Cross Axis<br>Sensitivity             | S                   | relative contribution<br>between any two of<br>the three axes                                  |             | 2         |          | %      |

| Alignment Error E <sub>A</sub> re     |                     | relative to package outline                                                                    | 10,         | 0.5       |          | 0      |

BST-BMA400-DS000-00 | Version 0.1 | November 2017

Page 10 / Confidential

### 2. Absolute maximum ratings

#### **Absolute maximum ratings**

| Parameter                   | Condition                    | Min  | Max                 | Units |

|-----------------------------|------------------------------|------|---------------------|-------|

| Voltage at Supply Pin       | V <sub>DD</sub> Pin          | -0.3 | 3.6                 | V     |

|                             | V <sub>DDIO</sub> Pin        | -0.3 | 3.6                 | V     |

| Voltage at any Logic Pin    | Non-Supply Pin               | -0.3 | $V_{DDIO}$ +0.3, <4 | V     |

| Passive Storage Temp. Range | ≤ 65% rel. H.                | -50  | +150                | °C    |

| Mechanical Shock            | Duration ≤ 200µs             |      | 10,000              | g     |

|                             | Duration ≤ 1.0ms             |      | 2,000               | g     |

| 200                         | Free fall onto hard surfaces |      | 1.8                 | m     |

| ESD                         | HBM, at any Pin              |      | 2                   | kV    |

|                             | CDM                          |      | 500                 | V     |

| ×.0-                        | MM                           | 70   | 200                 | V     |

#### Note:

Stress above these limits may cause damage to the device. Exceeding the specified electrical limits may affect the device reliability or cause malfunction.

Page 11 / Confidential

### 3. Quick Start Guide

The purpose of this chapter is to help developers who want to start working with the BMA400 by giving you some very basic hands-on application examples to get started.

#### Note about using the BMA400:

- The communication between application processor AP and BMA400 will happen either over I2C or SPI interface. For more information about the interfaces, read the related chapter 6. Digital Interfaces.

- For information about connecting the BMA400 to the host (AP), read the related chapter 7 where you find Pin-out and Connection Diagrams.

### First application setup examples algorithms:

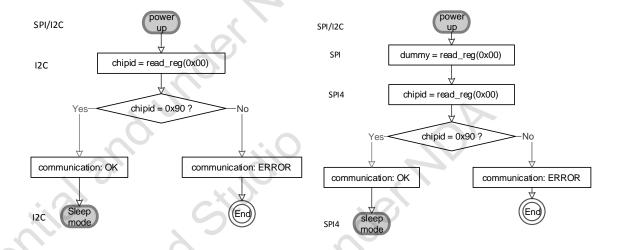

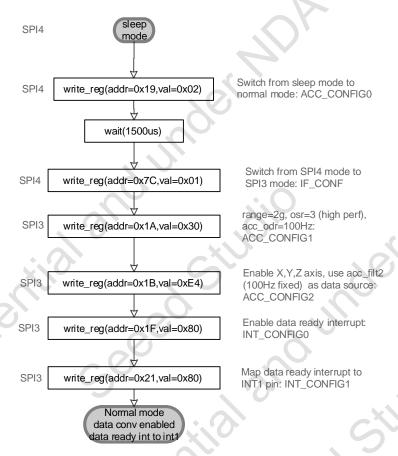

After correct power up by setting the correct voltage to the power pins, the BMA400 enters automatically into the Power On Reset (POR) sequence, also called boot sequence. After having completed boot, the BMA400 enters sleep mode where it consumes 200nA. No data conversions happen in this phase, but register read-out and write is possible. Communication can start in I2C or SPI mode. The BMA400 automatically detects which format is used. When SPI format is used, the BMA400 switches to SPI4 mode and remains in this mode until reset. The switching to SPI requires to send the very first SPI packet twice: the first packet will be ignored by the BMA400. If SPI3 communication is desired, a write to register IF\_CONF (write\_reg(IF\_CONF, 0x01)) switches the communication protocol to SPI3.

In order to properly make use of the BMA400, certain steps from host processor side are needed. The most typical operations will be explained in the following application examples in form of flow-diagrams.

Page 12 / Confidential

1. Example 1: Testing communication with the BMA400, switch to SPI communication, state data conversion, enable data ready interrupt and map it to INT1 pin

-reading chip id (checking correct communication) using I2C or SPI

Page 13 / Confidential

-switching from sleep to normal mode, then SPI3 mode, then enable data ready interrupt and map to pin int1

Page 14 / Confidential

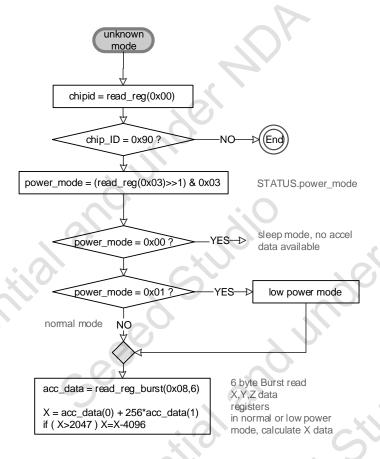

-checking communication via chipid, check power mode, read acceleration data if not in sleep mode

Page 15 / Confidential

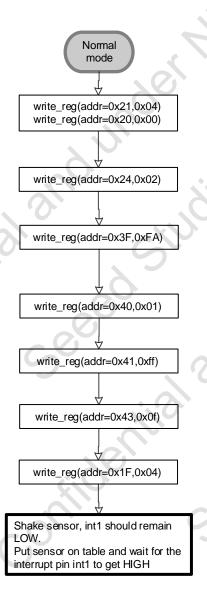

#### 1. Example 3: Testing interrupt engine of BMA400 (example: inactivity interrupt)

a. -performing reconfiguration sequence (interrupt feature: significant motion)

all interrupts only available in normal mode except wake-up, data ready

map gen1 interrupt to int1 pin interrupts are non-latched: if interrupt reason vanishes, int1 is deasserted

Int1 pin interrupt = HIGH active

Enable X,Y,Z axis, data source = acc\_filt2 (fixed 100Hz), update reference every time, hysteresis= 48mg

Configure gen1 interrupt to inactivity (criterion=0), AND combination of all axes

set threshold LSBs

set min. duration LSBs to 15 ODR ticks

Enable gen1 interrupt in normal mode, mapped to int1 pin and configured as inactivity interrupt with 15ODR ticks minimum duration

BST-BMA400-DS000-00 | Version 0.1 | November 2017

Page 16 / Confidential

#### **Further steps:**

The BMA400 has many more capabilities that are described in this document and include FIFO, power saving modes, synchronization capabilities with host processor, data synchronization, many interrupts generation and more features like step counter, etc.

BST-BMA400-DS000-00 | Version 0.1 | November 2017

Page 17 / Confidential

### 4. Functional Description

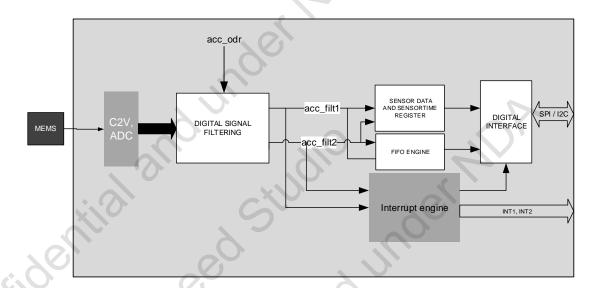

### **Block Diagram**

Page 18 / Confidential

#### 4.1. Supply Voltage and Power Management

BMA400 has two distinct power supply pins:

- VDD is the main power supply.

- VDDIO is a separate power supply pin used for supplying power for the digital communication interface.

There are no limitations with respect to the voltage level applied to the VDD and VDDIO pins, as long as it lies within the respective operating range. Furthermore, the device can be completely switched off (VDD=0V) while keeping the VDDIO supply within operating range or vice versa. However if the VDDIO supply is switched off, all interface pins (CSB, SDX, SCX) must be kept close to GNDIO potential. No constraints exist for the minimum slew-rate of the voltage applied to the VDD and VDDIO pins.

Page 19 / Confidential

#### 4.2. Power Modes - performance modes

The power mode and all major settings affecting performance, current consumption, noise and output data rate are controlled in registers ACC CONFIGO, ACC CONFIG1 and ACC CONFIG2.

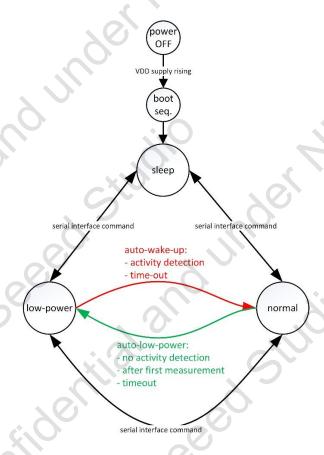

The BMA400 knows 3 power modes: sleep mode, low-power mode and normal mode.

In **sleep mode**, current consumption is below 300nA, and data conversions are stopped as well as sensortime functionality.

In **low power mode**, data conversion runs with a fixed rate of 25Hz, and performance can be controlled via ACC\_CONFIG0.osr\_lp setting. Current consumption ranges between 800 nA and 1100 nA depending on performance setting. The low power mode should be mainly used in combination with activity detection as self wake-up mode. In this use case, 800 nA are sufficient.

In **normal mode**, output data rates between 800Hz and 12.5Hz can be configured using the registers ACC\_CONFIG1.acc\_odr and ACC\_CONFIG1.osr. The noise density performance of the BMA400 is mainly determined by ACC\_CONFIG1.osr. The RMS noise and the resulting current consumption of the device is influenced by ACC\_CONFIG1.acc\_odr and ACC\_CONFIG1.osr.

Page 20 / Confidential

In all 3 power modes both register contents and FIFO contents are retained. FIFO readout can be done in normal mode only. The FIFO is written only in normal mode.

| ACC_CONFIG0. power_mode<1:0> | Description                                                     | Details                                                                                                                                                                                                                                                                                              |

|------------------------------|-----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| b00<br>b11                   | Sleep mode<br>(default state after power-up and<br>after reset) | I(VDD)< 300nA typ No sensortime, no FIFO read, no data conversions. Register and FIFO content retained, registers readable and writeable                                                                                                                                                             |

| b01 Low-power mode           |                                                                 | I(VDD)< 1.1uA typ  Data conversion at 25Hz fixed, noise performance and current consumption tunable by ACC_CONFIG0.osr_lp setting wake-up interrupt to switch into normal mode  No FIFO read/write                                                                                                   |

| b10                          | Normal mode                                                     | I(VDD)< 14 uA typ  Data conversion configurable between 800Hz and 12.5Hz, noise performance and current consumption tunable by ACC_CONFIG1.osr FIFO read and write All interrupts available  Auto-low-power function/interrupt using generic interrupt 1 to switch automatically into low-power mode |

Page 21 / Confidential

#### Current consumption (uA) in normal mode and low-power mode

|                                                   | ACC_CONFIG1.osr or ACC_CONFIG0.osr_lp |     |    |     |

|---------------------------------------------------|---------------------------------------|-----|----|-----|

|                                                   | 11                                    | 10  | 01 | 00  |

| Normal mode ACC_CONFIG0. power_mode<1:0> = b10    | 14                                    | 8   | 5  | 3   |

| Low-power mode ACC_CONFIG0. power_mode<1:0> = b01 | 1.2                                   | 1.1 | 1  | 0.9 |

Noise performace (rms in mg) in normal mode and low-power mode in 4g range (x and y axes are shown, Z-axis is 1.27 x higher)

|                                                         | (3)      |      | ACC_CONFIG1.osr or<br>ACC_CONFIG0.osr_lp |      |       |  |  |

|---------------------------------------------------------|----------|------|------------------------------------------|------|-------|--|--|

| (8)                                                     | ODR [Hz] | 11   | 10                                       | 01   | 00    |  |  |

| 601                                                     | 800      | 4.41 | 6.23                                     | 8.81 | 12.48 |  |  |

|                                                         | 400      | 3.12 | 4.41                                     | 6.23 | 8.81  |  |  |

| Normal mode                                             | 200      | 2.21 | 3.12                                     | 4.41 | 6.23  |  |  |

| ACC_CONFIGO. power mode<1:0> = b10                      | 100      | 1.56 | 2.21                                     | 3.12 | 4.41  |  |  |

|                                                         | 50       | 1.09 | 1.56                                     | 2.21 | 3.12  |  |  |

|                                                         | 25       | 0.78 | 1.09                                     | 1.56 | 2.21  |  |  |

| 6/0                                                     | 12.5     | 0.55 | 0.78                                     | 1.09 | 1.56  |  |  |

| Low-power mode<br>ACC_CONFIGO.<br>power mode<1:0> = b01 | 25       | 4.41 | 6.23                                     | 8.81 | 12.48 |  |  |

Page 22 / Confidential

#### Wake-up Interrupt / Auto wake-up

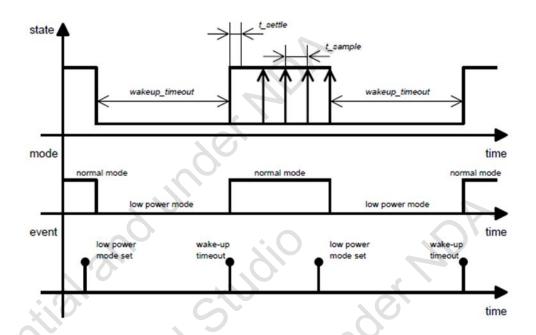

The auto-wakeup function is part of the power management concept of the BMA400. If the wakeup function (only available in low-power mode) changes the power mode to "normal", the host processor can be notified by an interrupt. This is called "wakeup interrupt", thus, the two topics "auto wakeup" and "wakeup interrupt" are handled together in this chapter.

The transition from Low-power to Normal mode is named "wake-up".

Switching into Normal mode from Low-power mode can be explicitly triggered by a serial interface command. This can also be done automatically by using the auto wakeup function.

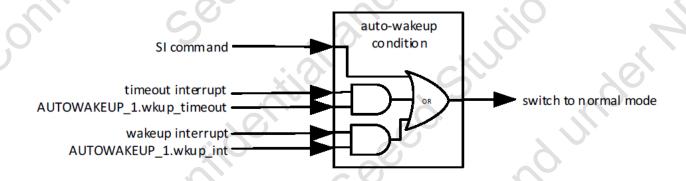

Auto wakeup can be either timer triggered or activity triggered. Each selected condition is independent and can be used as wake-up condition. In case more than one condition is selected, the first occurred condition sets the BMA400 into normal mode.

The three possible triggers for wake-up from low-power mode are:

- by serial command (already described in a previous chapter)

- by timeout

- by activity

#### Wakeup by timeout

The source condition wkup\_timeout and the timeout counter threshold value AUTOWAKEUP\_1.wakeup\_timeout\_thres is configured in register AUTOWAKEUP(0/1).

The wakeup\_timeout\_thres has 12bits for configuration of counter duration, with a resolution of 2.5ms/LSB. The maximum timeout for wake-up is 10.24s (4096\*2.5ms).

Page 23 / Confidential

#### Wake-up interrupt on activity

If in low-power mode, BMA400 will wake up when the conditions as defined by the configuration registers are fulfilled. The wake-up can be used for the wake-up of the external MCU using interrupt mapping or/and for changing the BMA400 power mode into normal mode to evaluate the acceleration data more accurately for complex/advanced interrupts or/and store the data in the FIFO for advanced processing on the external MCU.

The Low-power wake-up function evaluates acceleration data and is set as soon as the value of the sampled data exceeds the preconfigured acceleration threshold. The comparison of the current acceleration value with a reference is configurable between relative reference (last sampled value stored in the register) and absolute reference (the reference values are set once and not changing after each acceleration conversion). The delay between two data conversions is 40ms (25Hz conversion ODR in Low-power). The Low-power wake- up function is activated by setting AUTOWAKEUP\_1.wkup\_int bit. The wakeup status is available in INT\_STATO.wkup\_int. When woken up, an interrupt can be generated and mapped to the interrupt pins.

The Low-power wake-up function supports following configurations:

Selectable axis for wake-up: the Low-power wake-up function supports independent activation/deactivation of each acceleration axis for function evaluation. This is performed by setting the bits WKUP\_INT\_CONGIF0.wkup\_X/Y/Z\_en accordingly.

Page 24 / Confidential

Reference update mode (configured by setting WKUP\_INT\_CONFIG0.wkup\_refu)

| wkup_refu<1:0> | description of auto-wake references update mode                                                                                                   |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| b00            | manual update The references (int_wkup_refX/Y/Z) are not updated automatically, they shall be set manually by user                                |

| b01            | one time The references is updated every time at entering low power mode. The first measured acceleration in Low-power mode is used as reference. |

| b10 or b11     | every time The reference is updated every time after the acceleration conversion in low-power mode                                                |

The reference values are 8-bit signed values. The activity measurement takes the upper 8 bits of the acceleration value and compares against the reference WKUP\_INT\_CONFIG[2-4].int\_wkup\_ref[x,y,z].

- Threshold for activity detection: the threshold for activity detection (comparison of the difference between the measured acceleration data and reference acceleration data) has 8-bit resolution, corresponding to the upper 8 bits of the absolute value of the 12bit acceleration, WKUP\_INT\_CONFIG1.int\_wkup\_thres.

- Number of samples for decision: the number of samples for wake-up decision is configured between 1 and 8 by the register WKUP\_INT\_CONFIGO. num\_of\_samples (number of samples is the register value + 1).

The condition for activity-driven automatic wake-up from low-power is (assuming all 3 axes are enabled):

( abs(a\_x-ref\_x) > thresh\_x ) OR ( abs(a\_y-ref\_y) > thresh\_y ) OR( abs(a\_z-ref\_z) > thresh\_z ) This condition must persist for WKUP\_INT\_CONFIG0. num\_of\_samples data samples.

BST-BMA400-DS000-00 | Version 0.1 | November 2017

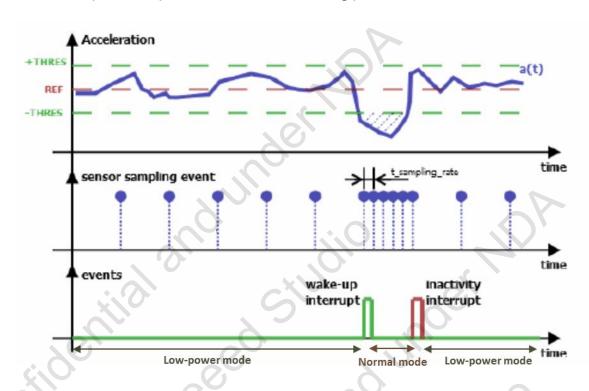

The wake-up on activty is illustrated in the following picture

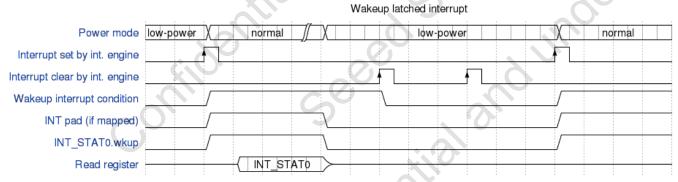

Wake-up interrupts can be used latched and non-latched (see chapter TBD). Latched and non-latched behavior is shown below.

Pin == INT\_STAT0.wkup. INT\_STAT0 cleared by read

Page 26 / Confidential

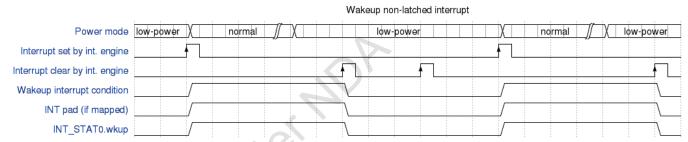

Pin and INT\_STAT0.wkup == interrupt condition. Interrupt evaluated in low-power mode only. Read INT\_STAT0 has no effect

#### Auto low-power mode

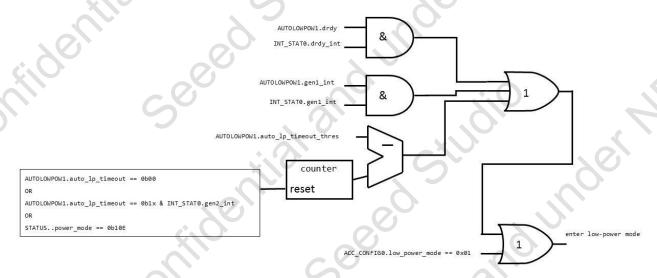

Power mode can be changed from Normal to Low-power mode through a serial interface command. It is also possible to change automatically (without a serial command) from normal mode to low-power mode, called auto low-power.

The following timed and non-timed triggers are supported for automatic switching from Normal mode to Low-power mode:

- First data ready: (AUTOLOWPOW\_1.auto\_lp\_timeout =b00)

If AUTOLOWPOW\_1.drdy = '1', BMA400 is set into low-power mode when new data calculation is finished.

- Generic interrupt 1: (AUTOLOWPOW\_1.auto\_lp\_timeout =b00)

If AUTOLOWPOW\_1.gen1\_int = '1', BMA400 is set into Low-power mode as soon as the Generic interrupt 1 is detected. (see chapter 4.6)

- low\_power\_timeout (AUTOLOWPOW\_1.auto\_lp\_timeout =b01): the sensor is set into low-power mode as soon the timeout counter reaches AUTOLOWPOW\_1.auto\_lp\_timeout\_thres. The auto-low-power timeout counter is 12 bits wide and is incremented every 2.5ms.

- low\_power\_timeout with counter reset on activity detected (AUTOLOWPOW\_1.auto\_lp\_timeout =b10,b11): the timeout counter is restarted in case generic interrupt 2 (see chapter 4.6) is asserted.

- The sensor is set into low-power mode when finally the timeout counter reaches AUTOLOWPOW\_1.auto\_lp\_timeout\_thres. The auto-low-power timeout counter is 12 bits wide and is incremented every 2.5ms.

Page 27 / Confidential

The timed timeout trigger can be configured by setting AUTOLOWPOW\_1.auto\_lp\_timeout bits in register according to the table below.

| AUTOLOWPOW_1.auto_lp<br>_timeout<1:0> | Description                                                                                                                |

|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| b00                                   | timeout disabled, use either AUTOLOWPOW_1.drdy or AUTOLOWPOW_1.gen1_int to switch automatically into low-power mode        |

| b01                                   | timeout active, BMA400 switching into low-power mode as soon as timeout counter reaches AUTOLOWPOW_1.auto_lp_timeout_thres |

| b10 or b11                            | Low-power timeout active, timeout counter resets on activity detection                                                     |

Multiple selections of auto-low-power conditions are supported. Any selected condition switches the device into low-power mode (OR condition). The logical connection of the auto-low-power conditions

Page 28 / Confidential

#### 4.3. Sensor Data

#### **Acceleration Data**

The width of acceleration data is 12 bits given in two's complement representation in the registers 0x04 to 0x09 (<u>ACC X LSB</u>, <u>ACC X MSB</u>, <u>ACC Y LSB</u>, <u>ACC Y MSB</u>, <u>ACC Z LSB</u>, <u>ACC Z MSB</u>). The 12 bits for each axis are split into an MSB upper part and an LSB lower part.

In order to ensure the integrity of the acceleration data read, the content of all data registers must be read in a single burst read, since these registers are write-protected during a read access. As soon as the burst read is finished the register content will be updated if new data are available.

#### **Filter Configuration**

Two major filter paths are implemented, see blockdiagram. Filter output can either be fed into the data registers, into the FIFO, or used to process interrupts in the interrupt engine. This is selectable by customer.

Filter1 (acc\_filt1) has a data rate between 800Hz and 12.5Hz, controlled by ACC\_CONFIG0.acc\_odr. Its bandwidth can be configured additionally by ACC\_CONFIG0.filt1\_bw:

- ACC\_CONFIG0.filt1\_bw =  $0x0 \rightarrow 0.48 \times ODR$

- ACC\_CONFIG0.filt1\_bw =  $0x1 \rightarrow 0.24 \times ODR$

| ACC_CONFIG0.acc_odr <3:0> | Output Data Rate [Hz] |

|---------------------------|-----------------------|

| 0xB 0xF                   | 800                   |

| 0xA 7                     | 400                   |

| 0x9                       | 200                   |

| 0x8                       | 100                   |

| 0x7                       | 50                    |

| 0x6                       | 25                    |

| 0x0 0x5                   | 12.5                  |

Filter2 (acc filt2) has a fixed data rate of 100 Hz.

In addition, these 100 Hz data is used by a third filter and filtered with a bandwidth of 1 Hz. The output data rate will stay at 100 Hz. This data can be used as input for the data registers and also in the interrupt engine. Access via FIFO is not possible.

| ACC_CONFIG2.data_src_reg<1:0> | Filter output going into data registers (not FIFO!) |

|-------------------------------|-----------------------------------------------------|

| 0x0,0x3                       | acc_filt1(selectable ODR)                           |

| 0x01                          | acc_filt2 (100Hz ODR)                               |

| 0x02                          | acc_filt_lp (1 Hz BW, 100 Hz ODR)                   |

| FIFO_CONFIG0.fifo_data_src | Filter output going into FIFO |

|----------------------------|-------------------------------|

| 0x0                        | acc_filt1(selectable ODR)     |

| 0x1                        | acc_filt2 (100Hz ODR)         |

BST-BMA400-DS000-00 | Version 0.1 | November 2017

Page 29 / Confidential

In low-power mode, only data at 25Hz ODR is available. Depending on the setting of ACC\_CONFIG0.osr\_lp, noise and current consumption is controllable.

#### G-range selection

The measurement g-range can be selected between 2g and 16g. It can be configured ACC\_CONFIG1.acc\_range.

| ACC_CONFIG1.acc_range<1:0> | Selected g-range |

|----------------------------|------------------|

| 11                         | 16g              |

| 10                         | 8g               |

| 01                         | 4g               |

| 00                         | 2g               |

#### **Data Ready Interrupt**

This interrupt fires whenever a new data sample set is complete. This allows a low latency data readout, especially avoiding to interfere with front-end conversion activity. In non-latched mode, the interrupt and the flag in Register <a href="INT STATO">INT STATO</a> are cleared automatically after 1/(1600Hz). If this automatic clearance is unwanted, latched-mode can be used.

In order to enable/use the data ready interrupt map it on the desired interrupt pin via <a href="INT1 MAP">INT1 MAP</a> or <a href="INT2 MAP">INT2 MAP</a>.

#### **Temperature Sensor**

The temperature sensor has 8 bits resolution. The temperature value is defined in Register TEMP DATA and updated every 160ms.

It is always on when the sensor is active (in normal and in low-power mode, not in sleep mode).

| Value | Temperature |          |

|-------|-------------|----------|

| 0x7F  | 87.5 °C     | \ '      |

|       | •••         | . 0      |

| 0x02  | 25 °C       | XII      |

|       |             |          |

| 0x80  | -40.0 °C    | <b>5</b> |

The temperature sensor is calibrated with a precision of +/-5°C.

Page 30 / Confidential

#### **Sensor Time**

The BMA400 has an integrated sensor timer. The sensor time can be used for synchronization purposes between the external MCU and the sensor.

The sensor timer counts the clock cycles generated by the system clock which is always running in low-power and normal modes. Sensor timer is inactive in sleep mode and reset when entering the sleep mode. Counter values are stored in registers SENSOR\_TIME(0/1/2).

The sensor timer has a resolution of 21 bits stored in 3 bytes. For compatibility with other sensors that use faster counters with 25.6 kHz, the lower three bits of the counter (sensor\_time<2:0>) are always 0. Thus, the lowest significant bit of the counter is sensor\_time<3>.

After the timer has reached the maximum value, the counter resets to zero.

| Bit <i>m</i> in sensor_time | 23     | 22     | 21    | 8   | 7   | 6   | 5     | 4     | 3      |

|-----------------------------|--------|--------|-------|-----|-----|-----|-------|-------|--------|

| Resolution [ms]             | 327.68 | 163.84 | 81.92 | 10  | 5   | 2.5 | 1.250 | 0.625 | 0.3125 |

| Update rate [Hz]            | 0.0031 | 0.0061 | 0.012 | 100 | 200 | 400 | 800   | 1600  | 3200   |

The sensortime is synchronized with the data capturing in the data register and the FIFO. The sensortime supports multiple seconds of sample counting and a sub-millisecond resolution.

Burst reads on the registers <u>SENSORTIME 0</u> to <u>SENSORTIME 2</u> deliver always consistent values, i.e. the value of the register does not change during the burst read.

Page 31 / Confidential

#### 4.4. FIFO

#### **FIFO description**

Acceleration data are stored in a 1024Bytes FIFO. The FIFO is written only in normal mode. When FIFO\_CONFIGO.fifo\_stop\_on\_full = '0', the device is in stream mode. When FIFO\_CONFIGO.fifo\_stop\_on\_full = '1', the device is in FIFO mode.

- Stream mode: overwrites oldest data on FIFO full condition

- FIFO full mode: discards newest data on FIFO full condition

The FIFO depth is 1024 byte and supports the following interrupts:

- FIFO full interrupt

- FIFO watermark interrupt

The data to be collected is defined through  $fifo_data_src$ ,  $fifo_x_en$ ,  $fifo_y_en$  and  $fifo_z_en$  bits. FIFO is disabled when no writing is defined; FIFO is therefore disabled when  $fifo_x_en=20$ ,  $fifo_y_en=20$  and  $fifo_z_en=20$ .

If the FIFO is disabled when FIFO byte count is greater than 0, no new frame is written to the FIFO, but FIFO is operational:

- Frames already written in the FIFO remain stored and can be read out

- FIFO interrupts and their corresponding statuses are still evaluated

- after all bytes are read out, sensortime (if enabled) and empty frames are generated

- FIFO can be flushed

#### FIFO input data

Storing of acceleration measurement results is enabled by setting respectively  $fifo_x_en = '1'$  and/or  $fifo_y_en = '1'$  and/or  $fifo_z_en = '1'$ . Storing of data can be enabled or disabled on a per-axis basis in any combination.

acc\_filt1 or acc\_flit2 data are stored in the FIFO depending on fifo\_data\_src bit.

Thus, the data rate with which data is stored in the FIFO equals the data rate with which the filter serving as data source is configured.

The number of bytes available in the FIFO is readable through fifo bytes cnt<10:0>.

The FIFO byte count registers FIFO\_LENGTH0 and FIFO\_LENGTH1 are updated only when a full frame has been written to the FIFO and is available for read-out. FIFO byte count registers are also updated after each fullframe read from the FIFO.

FIFO byte count registers increment or decrement is equal to the frame length; intermediate increments (corresponding to a partial frame) are not readable.

The FIFO shall support two modes for acceleration data storage in FIFO: 12 bits stored as two bytes into FIFO and 8-bit mode stored as single byte into FIFO per acceleration axis. The 8-bit mode activation shall be performed by setting FIFO CONFIGO.fifo 8bit en = '1'.

Page 32 / Confidential

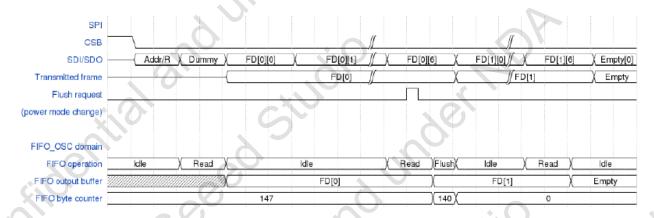

#### FIFO read out

The FIFO can be read out via FIFO\_DATA register in a single burst read, this allows a complete reading of the FIFO content within one burst read transaction.

FIFO read out is not supported in Sleep mode.

FIFO read out is supported in normal and Low-power mode if  $FIFO\_PWR\_CONFIG.fifo\_read\_en =$  '1'. The minimum delay  $T_{fifo\_read}$  has to be applied between the write command of  $FIFO\_PWR\_CONFIG.fifo\_read\_en =$  '1' and the start of FIFO read. Don't read the FIFO when  $FIFO\_PWR\_CONFIG.fifo\_read\_en =$  '0'.

#### FIFO overflow behavior

A FIFO overflow occurs if the FIFO is full and a new data is to be written to the FIFO. FIFO full means free space is less than maximum frame length of 9 bytes. The largest frame is 7 bytes long, however each time FIFO is written (at the end of the measurement), 9 bytes can be written to the FIFO in total, consisting of 2 frames: one with the measurement results (maximum of 7 bytes), and configuration change frame consisting of 2 bytes. The definition of the full interrupt uses 9 bytes limit to give the host system time to react to it before the FIFO overflows.

In case of overflow the FIFO can either stop recording data or overwrite the oldest data. The behavior is controlled by register *fifo\_stop\_on\_full*.

Streaming mode, *fifo\_stop\_on\_full* = '0': if the new frame does not fit inside the remaining free space in the FIFO RAM, FIFO will repeatedly delete the oldest frame until it creates enough space for the new one.

FIFO stop-on-full mode, fifo stop on full = '1': The newest frame is discarded.

Normal operation resumes if the FIFO full condition no longer persists.

Page 33 / Confidential

#### **Frames**

The FIFO captures data in frames, which consist of a header and a payload.

• Each data frame consists of a one byte header describing properties of the frame, (which data are included in this frame) and the data itself. Beside the data frames, there are control frames, sensortime frames and empty frames.

The header has a length of 8 bit and the following format:

| Bit    | 7      | 6       | 5             | 4 | 3 | 2 | 1 | 0 |

|--------|--------|---------|---------------|---|---|---|---|---|

| Header | fh_mod | le<1:0> | fh_param<4:0> |   |   |   | 0 |   |

fh\_mode and fh\_param<4> indicate whether the frame is a data frame (accel data), a sensortime frame (sensortime data), a control frame or an empty frame (all data 0).

A data frame is composed of the said header and a set of acceleration data organized as described in table below.

| Bit     | 7                                                                         | 6       | 5             | 4      | 3       |  | 2 | 1 | 0 |

|---------|---------------------------------------------------------------------------|---------|---------------|--------|---------|--|---|---|---|

| Header  | fh_mod                                                                    | le<1:0> | fh_param<4:0> |        |         |  |   | 0 |   |

| Data 17 | 1 7 Data bytes, number depending of 12 or 8bit storage mode and number of |         |               |        |         |  |   |   |   |

|         |                                                                           |         |               | axes e | nabled. |  | * |   |   |

These fh mode and fh parm fields are defined below

| fh_mode<1:0> | Definition        | fh_param <4>          | fh_param <3>                    | fh_param <2:0> |

|--------------|-------------------|-----------------------|---------------------------------|----------------|

| 0b10         | Sensor data frame | b0: Sensor data frame | b0: 8bit mode<br>b1: 12bit mode | Enabled axes   |

| 0b10         | sensortime frame  | b1: sensortime frame  | no meaning                      | No meaning     |

| 0b01         | Control frame     |                       | . 0                             | b0001          |

| Name    |           | fh_parm<2:0> |           |

|---------|-----------|--------------|-----------|

| Bit     | 2         | 1            | 0         |

| Content | z-enabled | y-enabled    | x-enabled |

f\_param<3:0>=0b0000 is invalid for regular mode, a header of 0x80 indicates an uninitialized frame.

In a data frame, fh\_param<2:0> defines which sensors axes are included in the data part of the frame. fh\_param<3> defines in which resolution – 8 or 12bit – the data are stored.

BST-BMA400-DS000-00 | Version 0.1 | November 2017

<sup>©</sup> Bosch Sensortec GmbH reserves all rights even in the event of industrial property rights. We reserve all rights of disposal such as copying and passing on to third parties. BOSCH and the symbol are registered trademarks of Robert Bosch GmbH, Germany.

Note: Specifications within this document are subject to change without notice.

Page 34 / Confidential

fh\_param<2/1/0> indicate whether Z, y or x axis data are stored.

Thus, fh\_param<3:0> allows to calculate the amount of data payload following the header.

The maximal payload is 6 bytes if all axes are enabled and 12bits are stored.

3bytes payload are needed if all axes are enabled and 8bits are stored.

A lesser amount of data is required if one or two axes are disabled.

As an example, data frames with 12bit and 8bit resolution are shown below, all axes enabled

| Bit    | 7                             | 6   | 5   | 4        | 3          | 2          | 1     | 0 |

|--------|-------------------------------|-----|-----|----------|------------|------------|-------|---|

| Header | 1                             | 0   | 0   | 1: 12bit | 1: Z       | 1: Y       | 1: X  | 0 |

|        |                               | unu | sed |          |            | acc_x      | <3:0> |   |

|        | acc_x-                        |     |     |          | <11:4>     |            |       |   |

| data   | unused                        |     |     | (,(0)    | acc_y<3:0> |            |       |   |

|        | . 7                           |     |     | acc_y    | <11:4>     |            |       |   |

|        | unused acc_z<3:0> acc_z<11:4> |     |     |          |            | acc_z<3:0> |       |   |

|        |                               |     |     |          |            |            |       |   |

| Bit    | 7           | 6 | 5    | 4       | 3      | 2    | 1    | 0  |  |

|--------|-------------|---|------|---------|--------|------|------|----|--|

| Header | 1           | 0 | 0    | 0: 8bit | 1: Z   | 1: Y | 1: X | 0  |  |

|        | C           |   |      | acc_x<  | <11:4> | 8    |      |    |  |

| data   | acc_y<11:4> |   |      |         |        |      |      |    |  |

|        |             |   | Allo | acc_z<  | <11:4> | 2    |      | 70 |  |

A FIFO empty frame is a sensor data frame, this is what the header indicates (fh\_mode=b10). fh\_param<2:0>=b000 shows that the frame delivered is an empty frame and contains 1 data byte of value 0x00 after the header.

This kind of frame is delivered if the last frame in the FIFO was already read out or if the FIFO is empty. The format is shown below.

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|--------|---|---|---|---|---|---|---|---|

| Header | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Data   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

BST-BMA400-DS000-00 | Version 0.1 | November 2017

Page 35 / Confidential

If fh\_param<4:0>= b00000, the header indicates a sensor-time frame to come, its format shown below.

| Bit    | 7                  | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|--------|--------------------|---|---|---|---|---|---|---|--|--|

| Header | 1                  | 0 | 1 | 0 | 0 | 0 | 0 | 0 |  |  |

| time   | sensor_time<7:0>   |   |   |   |   |   |   |   |  |  |

|        | sensor_time<15:8>  |   |   |   |   |   |   |   |  |  |

|        | sensor_time<23:16> |   |   |   |   |   |   |   |  |  |

The data for the sensor-time frame consists of registers <code>sensor\_time2/1/0</code> at the moment the sensor-time frame transmission has started. A sensor-time frame is not stored in the FIFO, it is created on-the-fly and delivered with a FIFO burst read operation when all acceleration data frames have been transmitted and the burst read carries on requesting data.

The sensortime frame will only be delivered if fifo\_time\_en = '1'.

The already mentioned control frame looks as follows

| Bit    | 7 | 6 | 5 | 4 | 3 | 2              |    | 0 1             | 0                |

|--------|---|---|---|---|---|----------------|----|-----------------|------------------|

| Header | 0 | 1 | 0 | 0 | 1 | 0              |    | 0               | 0                |

| Opcode | 0 | 1 | 1 | 0 | 0 | acc_config1_cl | hg | acc_config0_chg | fifo_config0_chg |

- fifo\_config0\_chg = b1: The control frame will be inserted when FIFO\_CONFIG0.fifo\_data\_src change becomes active in FIFO.

- acc\_config0\_chg = b1: The control frame will be inserted when ACC\_CONFIG0.filt1\_bw change is valid for data stored in FIFO.

- acc\_config1\_chg: The control frame will be inserted when ACC\_CONFIG1.acc\_odr or ACC\_CONFIG1.osr or ACC\_CONFIG1.acc\_range change is valid for data stored in FIFO.

If more changes become active at one acceleration sample just one control frame will be inserted, with more than one of the three CONF chg bits set.

The data format for data frames is identical to the format defined for the data registers: signed integer. If no axis is selected for FIFO storage no frames are written into the FIFO.

BST-BMA400-DS000-00 | Version 0.1 | November 2017

Page 36 / Confidential

#### **Under-read**

In case the FIFO is under-read (not all frames were taken from the FIFO, but the last frame read was read entirely), the next readout will continue at the frame that was just about to be sent.

#### Partial frame read

In case the FIFO is under-read and a partial data frame read occurred (not all frames were taken from the FIFO, and the last frame read was not read entirely), the entire last data frame is repeated upon the next read access.

When *fifo\_stop\_on\_full=*'0' oldest frames are overwritten when new frames are available and the FIFO is full.

When this happens, the partially read data frame is not repeated but the oldest frame available in the memory is sent instead.

Sensortime frame is not repeated when it is read only partially.

If the read of a frame is interrupted during the frame's last byte read, this partial read is not recognized and the frame is discarded like a fully read frame.

#### Over-read

If the burst read continues after all frames have been read out, a sensortime frame is sent after the FIFO becomes empty during a burst read operation if *fifo\_time\_en=*'1'. After that or when FIFO was completely read, the empty frame is returned as long as the burst read is active.

#### Reading nearly-empty FIFO

FIFO contains a reading cache buffer for a complete frame. When there is only one unread byte left in the reading buffer, the FIFO starts prefetching the next frame from the memory to be ready for burst reading if there is any further frame, or it evaluates itself as empty.

If new data frames/config frames are written to the FIFO before this reading event, the FIFO will behave as containing one further frame and the new frame will be made available for reading as the next frame. If new data/config frames are written to the FIFO after the moment when "only one unread byte is left in the buffer", then user will see the FIFO as empty after the current frame will be finished.

Page 37 / Confidential

#### FIFO flushing

A FIFO flush operation is executed when a *flush* command is written to the CMD register, when a soft-reset command is issued or when the device changes power mode and FIFO auto flush is enabled through *FIFO\_CONFIGO.auto\_flush* bit. For system simplicity a flush is executed as soon as possible. FIFO can be written or flushed at any time when FIFO is not read (*FIFO\_PWR\_CONFIG.fifo\_read\_en =* '0')

Flush operation does not depend on serial interface activity to finish. Power mode transition (or write) does not have to wait for the Flush to finish. Serial interface always reads what is in the FIFO at the moment the next frame is prepared for the output buffer. Empty frames are read if the FIFO was flushed during the transaction.

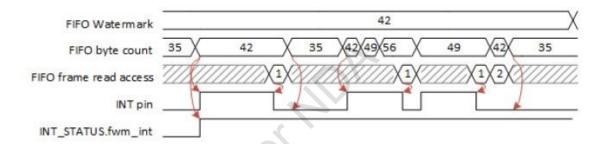

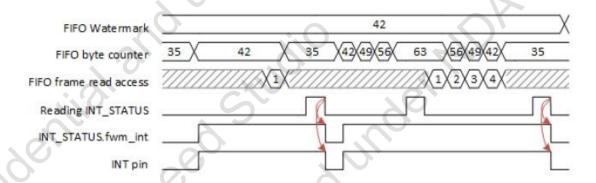

#### FIFO watermark interrupt

Watermark interrupt status is asserted when the watermark interrupt condition is satisfied i.e. when the filling level of the FIFO (number of unread bytes in the FIFO) is greater or equal to the watermark level ( $fifo\_bytes\_cnt<10:0> \ge fifo\_watermark<10:0>$ ). When the FIFO watermark level is set to zero, the interrupt condition is never satisfied. The status of the watermark interrupt can be read back through the  $fwm\_int$  bit.

Interrupt status is cleared by reading the *fwm\_int* bit when the FIFO filling level is lower than the watermark level. The watermark interrupt is propagated to INT1/2 pad only when it is enabled by setting bit *fwtm\_en* = '1'.

The interrupt is only evaluated after entire frames have been read out or written (as the counter is only in-/decreased on a frame basis).

Watermark interrupt condition is also updated after the end of the serial interface (burst read) transaction which wrote into the registers *fifo\_watermark<10:8>* or *fifo\_watermark<7:0>*.

The behavior of the FIFO watermark is shown in the figures below.

Page 38 / Confidential

FIFO watermark interrupt, non-latched, with reads from FIFO

FIFO watermark interrupt, latched, with reads from FIFO

Page 39 / Confidential

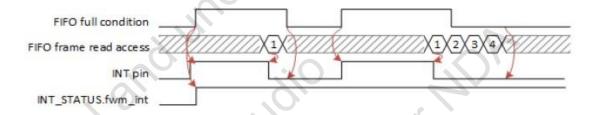

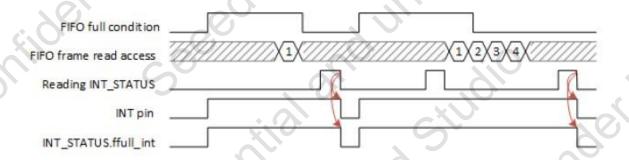

#### FIFO full interrupt

Full interrupt status is asserted when the full interrupt condition is satisfied, when the filling level of the FIFO (number of unread bytes in the FIFO = fifo\_bytes\_cnt<10:0>) is equal or higher than 1016. The status of the full interrupt can be read back through the ffull int bit.

Interrupt status is cleared by reading the *ffull\_int* bit high '1' when the FIFO filling level is lower than 1016.

The full interrupt is propagated to INT pad only when it is enabled by setting bit  $ffull\_en = '1'$ . The behavior of the FIFO full interrupt is shown in the figures below.

FIFO full interrupt, non-latched, with reads from FIFO

FIFO full interrupt, latched, with reads from FIFO

Page 40 / Confidential

#### 4.5. General Interrupt Pin configuration

#### **Interrupt Pin Mapping**

The content of the interrupt status registers can be mapped to pins INT1 or INT2, by setting the corresponding bits from the registers <a href="INT1 MAP">INT1 MAP</a>, respectively <a href="INT2 MAP">INT2 MAP</a> or <a href="INT12 MAP">INT12 MAP</a>.

To disconnect the features outputs to the external pins, the same corresponding bits must be reset, from the registers, <u>INT1 MAP</u>, respectively <u>INT2 MAP</u>.

Once a feature triggered the output pin, the Host can read out the corresponding bit from the register, <a href="INT\_STAT0">INT\_STAT1</a> or <a href="INT\_STAT1">INT\_STAT1</a> or <a href="INT\_STAT2">INT\_STAT1</a> or <a href="INT\_STAT2">INT\_STAT2</a>.

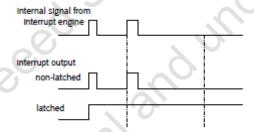

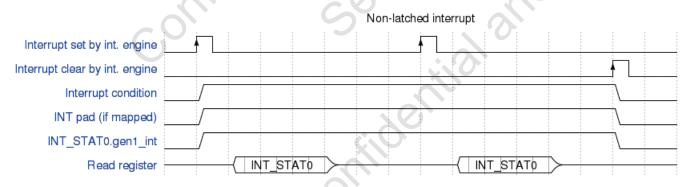

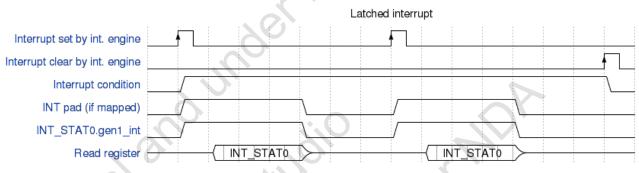

#### Interrupt latching

Interrupts can be configured as non-latched or latched. The mode is selected by <a href="INT\_CONFIG1.latch">INT\_CONFIG1.latch</a> int. Latching determines when an interrupt is released. The behavior of the different interrupt modes is shown graphically in the figure below

#### Non-latched mode

In the non-latched mode (<u>INT\_CONFIG1.latch\_int</u> = 0), both the INT pins (the contribution to the 'or' condition for the INT pin) and the interrupt status bit in INT\_STAT are reset when the interrupt activation condition is released.

Pin and INT\_STAT0.<int> == interrupt condition.

Page 41 / Confidential

#### Latched mode

In latched mode (<u>INT\_CONFIG1.latch\_int</u> = 1) an asserted interrupt status in INT\_STAT(0/1/2) and the INT pin (the contribution to the 'or' condition for the INT pin) is cleared by reading the corresponding status register. If the FIFO filling activation condition still holds true then the interrupt status is not cleared. Data ready and advanced interrupts' statuses are cleared upon reading INT\_STAT register.

Pin == INT STAT0.<int>, INT STAT0 cleared by read. Interrupt reasserts if condition still valid

#### Interrupt behavior during power mode switching

When the device leaves normal mode, all internal interrupt status registers are cleared. There are two exceptions:

- The step counter keeps its state (i.e. the step count) on mode switching. If the mode is switched to normal with enabled step counter, it continues counting on the previous value. The internal interrupt status is cleared.

- FIFO interrupts are not cleared by mode switching

Page 42 / Confidential

#### **Electrical Interrupt Pin Behavior**

Both interrupt pins INT1 and INT2 can be configured to show the desired electrical behavior.

The 'active' level of each interrupt pin is determined by the int1\_lvl and int2\_lvl bits.

If int1 | lvl = 1 / int2 | lvl = 1, then pin "INT1" / pin "INT2" are active HIGH.

The characteristic of the output driver of the interrupt pins is configured with bits *int1\_od* and *int2\_od*. By setting bits *int1\_od* / *int2\_od* to '1', the output drivers show open-drive characteristic, by setting the configuration bits to 0, the output drivers show CMOS push-pull characteristic.

When open-drive characteristic is selected in the design, an external pull-up or pull-down resistor should be applied according the int(1/2) IvI configuration.

For all interrupts, the user is responsible of the settings, no hardware checks of the settings are implemented before processing interrupts.

| int(1/2)_od | int(1/2)_lvl | "INT1" / "INT2" | output driver                         |

|-------------|--------------|-----------------|---------------------------------------|

| 0           | 0            | active '0'      | push-pull characteristic              |

| 0           | 1            | active '1'      | push-pull characteristic              |

| 1           | 0            | active '0'      | open-drive characteristic sink (NMOS) |

| 1           | 1            | active '1'      | open-drive characteristic source      |

Page 43 / Confidential

#### 4.6. Interrupt Features

The following interrupts exist in the BMA400:

#### Basic interrupts

- Data ready interrupt

- FIFO watermark

- FIFO full

- Interrupt engine overrun

- Wake-up interrupt

#### Advanced Interrupts

- Generic interrupt 1

- Generic interrupt 2

- Step detector interrupt/step counter

- Activity changed interrupt

- Single tap / Double tap sensing

- Orientation changed interrupt

Basic interrupts can all be enabled independently from each other.

Advanced interrupts are only available in normal mode, the interrupt engine is disabled in low power mode and sleep mode.

The interrupts served by the interrupt engine. They share the same resources and time-slices, thus, enabling too many interrupts of this type in parallel lead to a so-called Interrupt engine overrun. This interrupt indicating that the interrupt engine could not finish calculating all selected interrupt conditions. If this occurs, advanced interrupts of lesser importance must be disabled until the Interrupt engine overrun condition/interrupt vanishes.

Any change of an interrupt configuration must be executed when the corresponding interrupt is disabled.

Most interrupts require a data rate of 100Hz, only tap sensing requires 200Hz. It is then necessary to configure the data source of the tap sensing interrupt, filter acc\_filt1, to 200Hz, which implies that the other interrupts requiring 100Hz data rate use another filter.

#### Interrupt pin mapping, interrupt status

The BMA400 supports flexible INT1 and INT2 pin mapping configurations via interrupt mapping registers INT1\_MAP, INT2\_MAP and INT12\_MAP. Depending on these registers settings, all interrupt sources are mapped to the INT1 and INT2 pins.

The status of the interrupts can be read out at the status registers <u>INT\_STAT0</u>, <u>INT\_STAT1</u> and <u>INT\_STAT2</u>.

Additionally, the step counter value is stored in the registers <u>STEP CNTO</u>...<u>STEP CNT3</u>. These registers need to be read out using a burst read to avoid one register getting updated while another step count register is read.

Page 44 / Confidential

#### Generic Interrupt 1 and 2

The generic interrupts 1 and 2 have the exact same implementation. They are designed to detect activity or inactivity.

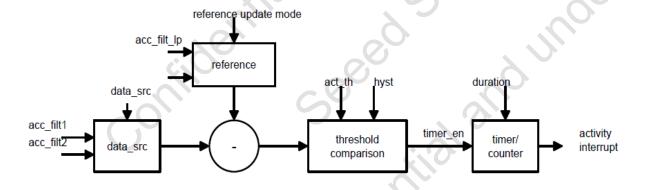

The generic interrupt monitors acceleration change with respect to a reference, or in other words, the difference between actual acceleration and reference is calculated and compared against a threshold. The comparison is de-noised using a hysteresis.

The generic interrupt is triggered when the above mentioned difference lasts for a minimum time.

Reference, threshold, hysteresis and duration are configurable.

Both generic interrupts work the same way, but have separate sets of registers to be processed independently of each other.

- Generic interrupt 1 is enabled by 'INT\_CONFIG0.gen1\_int\_en = 1'

- Generic interrupt 2 is enabled by 'INT CONFIG0.gen2 int en = 1'

The generic interrupt supports selectable acceleration axes for evaluation:  $GEN(1/2)INT\_CONFIG0.act\_(x/y/z)\_en$ .

$GEN(1/2)INT\_CONFIG1.comb\_sel$  selects if the interrupt shall be based on an AND ( $comb\_sel = 1$ ) or an OR ( $comb\_sel = 0$ ) combination of all enabled axes.

The acceleration data source is selectable between acceleration from *acc\_filt1* or *acc\_filt2* by setting GEN1/2INT CONFIGO. data src (0: acc\_filt1, 1:acc\_filt2).

The data rate for the filter output must be 100Hz. Using acc\_filt2 is recommended. In this case acc\_filt1 can be used independently from the interrupt engine for the data output registers and the FIFO.

Page 45 / Confidential

| GEN(1/2)INT_CONFIG0.data_src | Source for generic interrupt data |

|------------------------------|-----------------------------------|

| 0                            | acc_filt1                         |

| 1                            | acc_filt2                         |

The mentioned reference can be static (user defined) or it can be updated dynamically. The reference acceleration registers support reference update modes after comparison evaluation has been done. The mode is set in GEN(1/2)INT\_CONFIG0.act\_refu

| GEN(1/2)INT_CONFIG0.act_refu | Description of reference update mode                                                                                                                                                                                                                             |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| b00                          | no update – reference is statically set by user using GEN(1/2)INT_CONFIG4/5/6/7/8/9                                                                                                                                                                              |